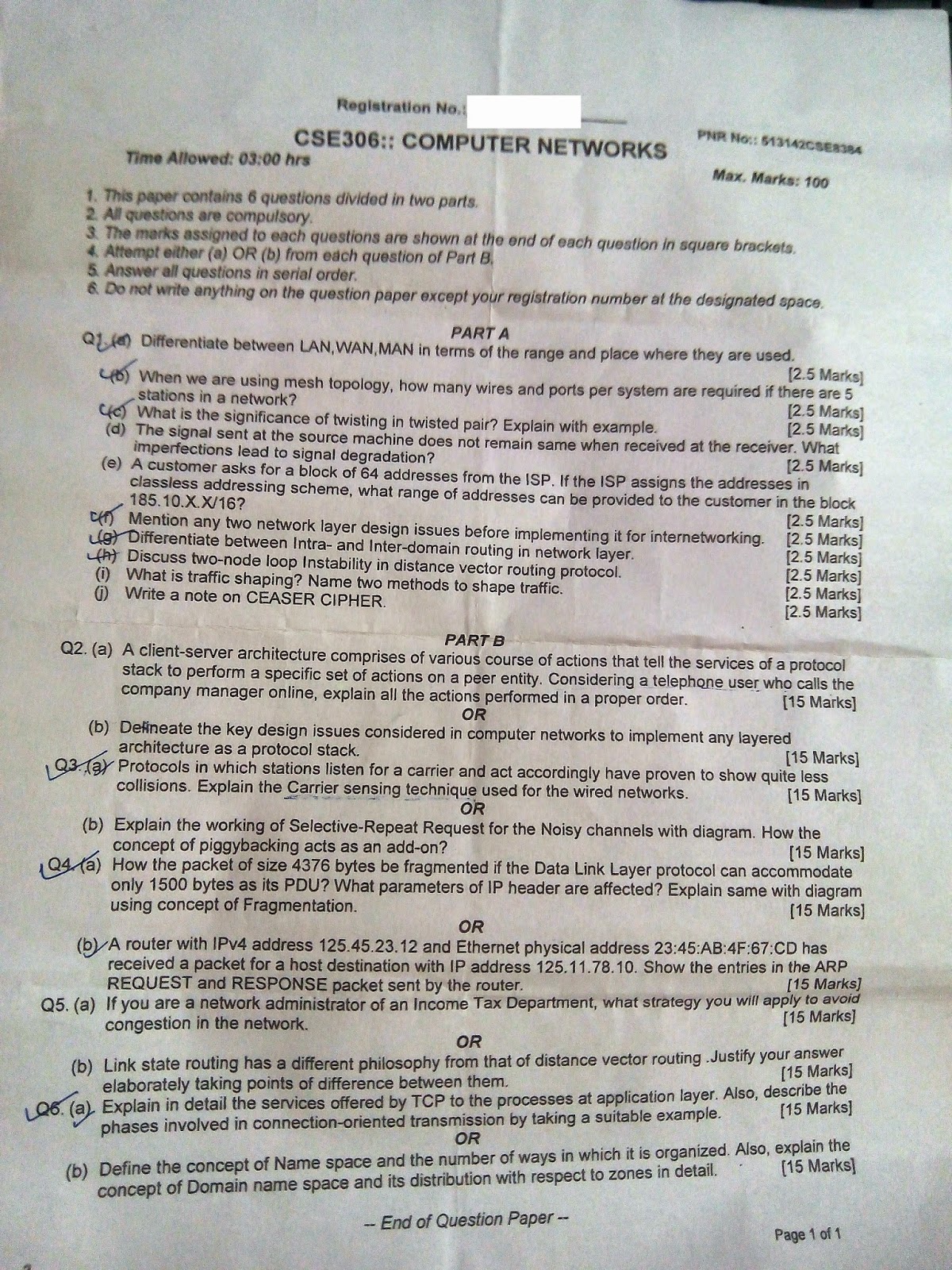

CSE306 COMPUTER NETWORKS

Course:CSE306::COMPUTER

NETWORKS

Time Allowed:

03:00 hrs Max. Marks: 100

1.

This paper contains 6 questions divided in two

parts.

2.

All questions are compulsory.

3.

The marks assigned to each questions are shown

at the end of the question in square brackets.

4.

Attempt either (a) OR (b) from each question of

Part B.

5.

Answer all the questions in serial order.

6.

Do not write anything on the question paper

except your registration number at the designated space.

PART A

Q1.

a)

Differentiate between LAN, WAN, MAN in terms of

the range and place where they are used.

b)

When we are using mesh topology, how many wires

and ports per system are required if there are 5 stations in a network?

c)

What is the significance of twisting in twisted

pair? Explain with example.

d)

The signal sent at the source machine does not

remain same when received at the receiver. What imperfections lead to signal

degradation?

e)

A customer asks for a block of 64 addresses from

ISP. If the ISP assigns the addresses in classless addressing scheme, what

range of addresses can be provided to the customer in the block classless

addressing scheme, what range of address can be provided to the customer in the

block 185.10.X.X/16?

f)

Mention ant two network layer design issues

before implementing it for internetworking.

g)

Differentiate between intra- and inter-domain

routing in network layer.

h)

Discuss two-node loop Instability in distance

vector routing protocol.

i)

What is traffic shaping? Name two methods to

shape traffic.

j)

Write a note on CEASER CIPHER.

PART B

Q2.

a)

A client-server architecture comprises of

various courses of actions that tell the services of a protocol stack to perform

a specific set of actions on a peer entity. Considering a telephone user who

calls the company manager online, explain all the actions performed in a proper

order.

OR

b)

Delineate the key design issues considered in

computer networks to implement any layered architecture as a protocol stack.

Q3.

a)

Protocols in which stations listen for a carrier

and act accordingly have proven to show quite less collisions. Explain the

Carrier sensing technique used for the wired networks.

OR

b)

Explain the working of Selective-Repeat Request

for the Noisy channels with diagram. How the concept of piggybacking acts as an

add-on?

Q4

a)

How the packet of size 4376 bytes be fragmented

if the Data Link Layer protocol can accommodate only 1500 bytes as its PDU?

What parameters of IP header are affected? Explain same with diagram using

concept of Fragmentation.

OR

b)

A router with IPV4 address 125.45.23.12 and

Ethernet physical address 23:45:AB:4F:67:CD has received a packet for a host

destination with IP address 125.11.78.10. Show the entries in the ARP REQUEST

and RESPONSE packet sent by the router.

Q5.

a)

If you are a network administrator of an income

tax department, what strategy you will apply to avoid congestion in the

network.

OR

b)

Link state routing has a different philosophy

from that of distance vector routing. Justify your answer elaborately taking

points of difference between them.

Q6.

a)

Explain in detail the services offered by TCP to

the processes at application layer. Also, describe the phases involved in

connection-oriented transmission by taking a suitable example.

OR

b)

Define the concept of Name space and the number

of ways in which it is organized. Also, explain the concept of Domain name

space and its distribution with respect to zones in detail.

--End of Question

Paper--

.png)